# LA RAM

La RAM comme Random Access Memory est indispensable pour que le PC fonctionne. Le processeur s'en sert pour stocker toutes les données qu'il a besoin pour faire ses calculs. Il stock les programmes actifs comme par exemple une fenêtre ouverte, l'anti-virus, les lettres tapées dans le bloc note pendant la rédaction d'un tex etc. Cette mémoire RAM est une mémoire type volatile (mémoire vive) c'est à dire qu'elle a besoin d'être alimentée en permanence pour garder l'information. C'est d'ailleurs pour cette raison que lorsque on éteint le PC en débranchant la prise par exemple et qu'on le rallume juste après, on recommence tout, on ne s'arrête pas où on en était.

Elles se présentent sous forme de barrettes de taille variable avec dessus quelques circuits intégrés généralement CMS (Composants Montées en Surface).

Il existe deux grandes familles de RAM: La RAM statique et le RAM dynamique.

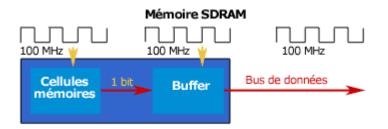

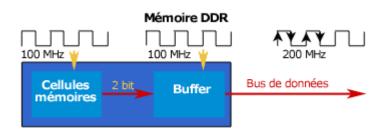

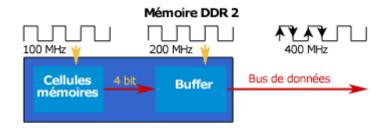

Il y a dans les RAM une zone buffer située entre les cellules mémoires et le bus qui sert à stocker des données temporairement, essentiellement entre deux processus avant de les écrire par bloc dans les cellules. L'objectif de l'écriture bufférisée est de profiter de la vitesse d'accès à la RAM pour minimiser ceux à des supports beaucoup plus lents. De cette manière, la mémoire écrit d'un coup les données. L'écriture bufférisée est gérer par un programme du système.

Certaines barrettes ont un bit de parité qui permettent d'assurer que les données n'ont pas d'erreur. Le bit de parité vaut 1 lorsque la somme des bits de donnée est impaire et 0 si la somme est paire. Toutefois, les bits de parité ne corrigent pas les erreurs.

Il existe des mémoires ECC (Error Correction Coding) qui possèdent plusieurs bits dédiés à la correction d'erreur (bits de contrôle). On trouve ce type de barrette essentiellement pour les serveurs.

La largeur des RAM peuvent être de 8, 16, 32 ou 64 bits.

## Les types de mémoire vive

### La mémoire dynamique

La mémoire dynamique **DRAM** est la plus courante mais a deux contraintes qui sont leur **petite vitesse** et leur **rafraîchissement**.

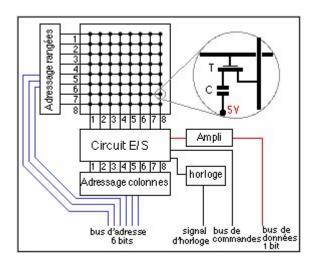

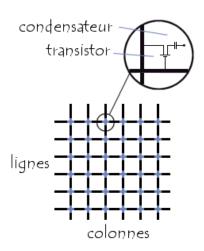

Leur faible vitesse de transfert sont dû au fait que pour stocker un bit, il faut un condensateur et un transistor à effet de champs qui commande ce condensateur. Si le condo est chargé, le bit vaut 1, si déchargé, le bit vaut 0. On appel cela une cellule. Les cellules sont organisées sous forme de matrice. On accède à une case mémoire par ligne et par colonne.

Chaque cellule a une adresse qui a un numéro de ligne et un numéro de colonne. Un accès à une case mémoire n'est bien évidement pas instantanée et demande un certain temps qu'on appel le temps de latence.

Il est possible d'exprimer ces temps de la mémoire dynamique à l'aide de quatre chiffres, comme par exemple: 2-3-3-3. Ces quatre chiffres ont une signification donnée ci-dessous :

1er chiffre, le CAS Delay : Concerne la lecture en mémoire. Désigne le nombre de cycles d'horloge nécessaires entre l'envoi de la commande de lecture et l'arrivée des données désirées.

2ème chiffre, le RAS Precharge Time : Nombre de cycles d'horloge nécessaires pour deux accès à une même ligne.

3ème chiffre, RAS to CAS: Nombre de cycles d'horloge nécessaires pour un accès d'une ligne à une colonne.

4ème chiffre, RAS Active Time : Nombre de cycles d'horloge nécessaires pour un accès à une ligne.

On distingue plusieurs types de mémoires dynamiques :

DRAM PM : Cette mémoire est l'une des première.

DRAM FPM (Fast Page Mode): Pour accélérer les accès à la mémoire, il existe une technique, appelée pagination consistant à accéder à des données situées sur une même colonne en modifiant uniquement l'adresse de la ligne, ce qui permet d'éviter la répétition du numéro de colonne entre la lecture de chacune des lignes. La FPM permet d'obtenir des temps d'accès de l'ordre de 70 à 80 ns pour une fréquence de fonctionnement pouvant aller de 25 à 33 Mhz.

DRAM EDO (Extended Data Out). La technique utilisée avec ce type de mémoire consiste à adresser la colonne suivante pendant la lecture des données d'une colonne. Cela créer un chevauchement des accès permettant de gagner du temps sur chaque cycle. Le temps d'accès à la mémoire EDO est donc d'environ 50 à 60 ns pour une fréquence de fonctionnement allant de 33 à 66 Mhz.

SDRAM: Cette mémoire (barrette de 168 contacts) est synchrone c'est à dire qu'elle se cadence à la vitesse du FSB, contrairement aux mémoires EDO et FPM (qualifiées d'asynchrones) possédant leur propre horloge. La SDRAM permet donc de s'affranchir des temps d'attente dus à la synchronisation avec la cartemère. Celle-ci permet d'obtenir un cycle en mode rafale de la forme 5-1-1-1, c'est-à-dire un gain de 3 cycles par rapport à la RAM EDO. De cette façon la SDRAM est capable de fonctionner avec une cadence allant jusqu'à 150 Mhz, lui permettant d'obtenir des temps d'accès d'environ 10 ns.

La DR-SDRAM ou RDRAM (Direct Rambus RAM) est un type de mémoire permettant de transférer les données sur un bus de 16 bits de largeur à une cadence de 800Mhz, (1,6 Go/s). Comme la SDRAM, ce type de mémoire est synchronisé avec l'horloge du bus pour améliorer les échanges de données.

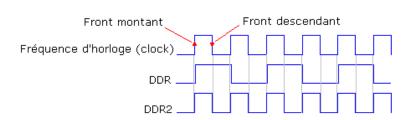

La DDR-SDRAM (Double Data Rate RAM) de 184 contacts ont la même technologie que les SDRAM et permettent de doubler le taux de transfert à fréquence égale en prenant en compte les fronts montants et descendants. Cette mémoire est alimentée en 2.5V.

La **DDR2-SDRAM** utilise un canal pour l'écriture et un autre pour la lecture disposant deux fronts d'horloge pour chacun d'eux. Elles ont 240 contacts et est alimentée en 1,8V.

DDR: changement d'état possible à chaque front montant DDR2: changement d'état possible à chaque front montant et descendant

On voit ici la différence entre la DDR et la DDR2

La **DDR3-SDRAM** est une amélioration de la DDR2 surtout en consommation électrique (40% inférieure) graçe à une baisse de la tension, elle est alimentée en 1,5V. Leurs transistors ont deux grilles. Les temps de latence sont restés un peu les mêmes par rapport à la DDR2. Les barrettes ont 240 contacts comme les DDR2 mais ne sont pas compatibles.

### La mémoire statique

Pour toutes les mémoires statiques, elles sont très rapides du fait qu'on ait pas de condensateur qui se charge ou se décharge, elles n'ont pas besoin d'être rafraîchit régulièrement. Il existe trois variantes de la mémoire vive statique:

**SRAM** (Static RAM): Cette mémoire utilise le principe de la **bascule** électronique, elle est très rapide et n'a pas besoin d'être rafraîchît régulièrement. On trouve ce type de mémoire incorporée dans un processeur qui lui permet de stocker les données importantes et très rapidement.

MRAM (Magnetic RAM): Cette mémoire stocke les données sous forme de charge magnétique. Elle utilise le principe de la magnétorésistance. Concrètement, les cellules de stockage sont composées de deux couches ferromagnétiques séparées par une fine couche isolante. Suivant l'orientation de l'aimantation des couches ferromagnétiques, la résistance va plus ou moins s'opposée au passage du courant. Le passage ou non de ce courant va déterminer si le bit est à 1 ou à 0, cette valeur peut-être lue par une tête ferromagnétique comme pour un disque dur.

**DPRAM** (Dual Ported RAM): Cette mémoire a la particularité d'avoir plusieurs accès presque simultanés en entrée et en sortie.

# Les détrompeurs

Chaque barrettes possèdent un détrompeur en fonction de son type afin de les différencier et de ne pas insérer une SD-RAM dans une DDR par exemple.

SD-RAM

Du haut en bas : DDR, DDR2 et DDR3

#### Le format des barrettes

Les barrettes ont plusieurs formes, plusieurs tailles :

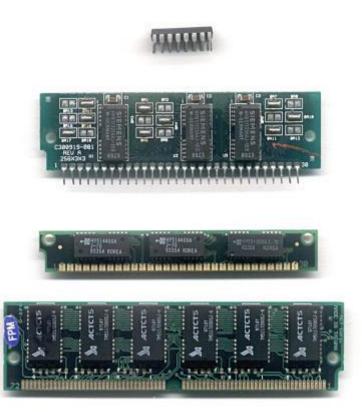

Les mémoires vives **DIP** (Dual Inline Package) sont les circuits intégrés basiques, composants traversants. Sur de très vieilles cartes mères, on les fixe sur un support permettant de les changer facilement.

Les barrettes **SIP** (Single Inline Package) ont généralement quelques circuits intégrés en boîtier DIP sur leur surface, leurs pattes dépassent du circuit imprimé et sont alignées.

Il y a eu les **SIMM** (Single Inline Memory Module) dont une des face possède les circuits intégrés. Il y a les SIMM a **30 connecteurs** et les SIMM à **72 connecteurs**.

Ensuite, pour les mémoires 64 bits, est apparu le format **DIMM** (Dual Inline Memory Module) dont les barrettes possèdent leurs circuits intégrés des deux côtés de la barrette avec 84 connecteurs de chaque côté. Ces mémoires possèdent un second détrompeur (SD-RAM).

Pour les PC portables, il y a les **SO DIMM** (Small Outline DIMM), elles possèdent 144 pins pour les 64 bits et 77 pins pour les 32 bits.

Les **RIMM** (184 pins) ressemblent au DIMM mais n'ont pas le même nombre de broches, elles possèdent généralement un dissipateur car elles ont une vitesse de transfert élevée (DDR3).

Il existe aussi les **SO-RIMM** pour les PC portables qui ont 160 broches.

De haut en bas : DIP, SIP, SIMM 30 pins, SIMM 72 pins , DIMM, RIMM

# Brochage d'une RAM SIMM30 :

| Pins | Fonctions  | Decription                      |

|------|------------|---------------------------------|

| 1    | VCC        | +5V                             |

| 2    | /CAS       | Sélection des colonnes          |

| 3    | DQ0        | Bit de données O                |

| 4    | <b>A</b> 0 | Adresse 0                       |

| 5    | <b>A</b> 1 | Adresse 1                       |

| 6    | DQ1        | Bit de données 1                |

| 7    | A2         | Adresse 2                       |

| 8    | <b>A</b> 3 | Adresse 3                       |

| 9    | GND        | Masse                           |

| 10   | DQ2        | Bit de données 2                |

| 11   | A4         | Adresse 4                       |

| 12   | <b>A</b> 5 | Adresse 5                       |

| 13   | DQ3        | Bit de données 3                |

| 14   | <b>A</b> 6 | Adresse 6                       |

| 15   | Α7         | Adresse 7                       |

| 16   | DQ4        | Bit de données 4                |

| 17   | A8         | Adresse 8                       |

| 18   | A9         | Adresse 9                       |

| 19   | A10        | Adresse 10                      |

| 20   | DQ5        | Bit de données 5                |

| 21   | /WE        | Autorisation d'écriture         |

| 22   | GND        | Masse                           |

| 23   | DQ6        | Bit de données 6                |

| 24   | n/c        | Non connecté                    |

| 25   | DQ7        | Bit de données 7                |

| 26   | QP         | Sortie de parité                |

| 27   | /RAS       | Sélection des lignes            |

| 28   | /CASP      | Sélection des colonnes (parité) |

| 29   | DP         | Entrée de parité                |

| 30   | VCC        | +5V                             |

# Brochage d'une RAM SIMM72 :

| Pins | Fonctions                                         | Decription                   |

|------|---------------------------------------------------|------------------------------|

| 1    | VS5                                               | Masse                        |

| 2    | DQ0                                               | Bit de données O             |

| 3    | DQ18                                              | Bit de données 18            |

| 4    | DQ1                                               | Bit de données 1             |

| 5    | DQ19                                              | Bit de données 19            |

| 6    | DQ2                                               | Bit de données 2             |

| 7    | DQ20                                              | Bit de données 20            |

| 8    | DQ3                                               | Bit de données 3             |

| 9    | DQ21                                              | Bit de données 21            |

| 10   | VCC                                               | Tension +5V                  |

| 11   | Non utilisé                                       | Non utilisé                  |

| 12   | AO                                                | Adresse 0                    |

| 13   | A1                                                | Adresse 1                    |

| 14   | A2                                                | Adresse 2                    |

| 15   | <b>A</b> 3                                        | Adresse 3                    |

| 16   | A4                                                | Adresse 4                    |

| 17   | <b>A</b> 5                                        | Adresse 5                    |

| 18   | <b>A6</b>                                         | Adresse 6                    |

| 19   | A10                                               | Adresse 10                   |

| 20   | DQ4                                               | Bit de données 4             |

| 21   | DQ22                                              | Bit de données 22            |

| 22   | DQ5                                               | Bit de données 5             |

| 23   | DQ23                                              | Bit de données 23            |

| 24   | DQ6                                               | Bit de données 6             |

| 25   | DQ24                                              | Bit de données 24            |

| 26   | DQ7                                               | Bit de données 7             |

| 27   | DQ25                                              | Bit de données 25            |

| 28   | A7                                                | Adresse 7                    |

| 29   | A11                                               | Adresse 11                   |

| 30   | VCC                                               | Tension +5V                  |

| 31   | A8                                                | Adresse 8                    |

| 32   | A9                                                | Adresse 9                    |

| 33   | /RA53                                             | Sélection de rangées 3       |

| 34   | /RAS2                                             | Sélection de rangées 2       |

| 35   | Non utilisé ou PQ 26 si le module est avec parité | Bit de données 26 (parité 3) |

| 36   | Non utilisé ou PQ 8 si le module est avec parité  | Bit de données 8 (parité 1)  |

| 37   | Non utilisé ou PQ 17 si le module est avec parité | Bit de données 17 (parité 2) |

| 38   | Non utilisé ou PQ 35 si le module est avec parité | Bit de données 35 (parité 4) |

| 39   | VSS                                               | Masse                        |

| 40   | /CASO                                             | Sélection de colonnes 0      |

| 41   | /CAS2                                             | Sélection de colonnes 2      |

| 42   | /CAS3                                             | Sélection de colonnes 3      |

| 43   | /CAS1                                             | Sélection de colonnes 1      |

| 44   | /RASO                                             | Sélection de rangées 0       |

| 45   | /RAS1                                             | Sélection de rangées 1       |

| La RAM | Sulivan F4FGV        |

|--------|----------------------|

|        | http://f0fgv.free.fr |

| 46 | Non utilisé | Non utilisé             |

|----|-------------|-------------------------|

| 47 | /WE         | Autorisation d'écriture |

| 48 | Non utilisé | Non utilisé             |

| 49 | DQ9         | Bit de données 9        |

| 50 | DQ27        | Bit de données 27       |

| 51 | DQ10        | Bit de données 10       |

| 52 | DQ28        | Bit de données 28       |

| 53 | DQ11        | Bit de données 11       |

| 54 | DQ29        | Bit de données 29       |

| 55 | DQ12        | Bit de données 12       |

| 56 | DQ30        | Bit de données 30       |

| 57 | DQ13        | Bit de données 13       |

| 58 | DQ31        | Bit de données 31       |

| 59 | VCC         | Tension +5V             |

| 60 | DQ32        | Bit de données 32       |

| 61 | DQ14        | Bit de données 14       |

| 62 | DQ33        | Bit de données 33       |

| 63 | DQ15        | Bit de données 15       |

| 64 | DQ34        | Bit de données 34       |

| 65 | DQ16        | Bit de données 16       |

| 66 | Non utilisé | Non utilisé             |

| 67 | PD1         | Détection de présence 1 |

| 68 | PD2         | Détection de présence 2 |

| 69 | PD3         | Détection de présence 3 |

| 70 | PD4         | Détection de présence 4 |

| 71 | Non utilisé | Non utilisé             |

| 72 | VSS         | Masse                   |

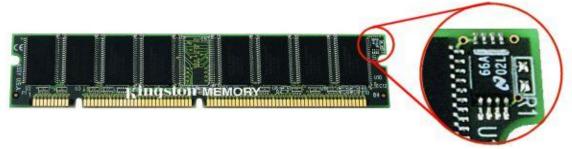

#### Le SPD

Le Bios de nos machines configure tout seul les timings des modules mémoires grâce à une puce d'EEPROM présente à même les barrettes : le SPD (Serial Presence Detect). Le Bios lit les informations présentes sur cette puce (capacité, fréquence, latence, mais aussi constructeur, numéro de série etc) au démarrage de l'ordinateur afin de régler les paramètres de fonctionnement de la RAM.

Une extension du SPD, l'EPP arrive sur le marché des mémoires haut de gamme. Cette mémoire supplémentaire permet de stocker plus d'informations sur les possibilités des modules mémoire en ce qui concerne les fréquences et les latences possibles. Ce qui permet d'utiliser les mémoires en overclocking automatique accessible par tout un chacun. Il faut pour cela des modules mémoires EPP avec un chipset autorisant l'EPP et activer l'option dans le Bios de la machine.

Le SPD, c'est un petit circuit intégré de 8 pattes, généralement situé dans un angle de la barrette